الشركة المصنعة لكابل البيانات عالية الجودة

الشركة المصنعة لكابل البيانات عالية الجودة

Epigraph: من 32GT/s إلى 64GT/s، قد يبدو الأمر وكأنه مجرد مضاعفة السرعة، ولكن وراء ذلك تحول كامل في المسار التقني.

المقدمة: أكثر من مجرد مضاعفة السرعة

بعد العمل في مجال خوادم الذكاء الاصطناعي ومراكز البيانات لسنوات عديدة، السؤال الذي يُطرح عليّ كثيرًا هو: ما الفرق الحقيقي بين PCIe 5.0 و6.0؟ أليس هذا مجرد مضاعفة السرعة؟

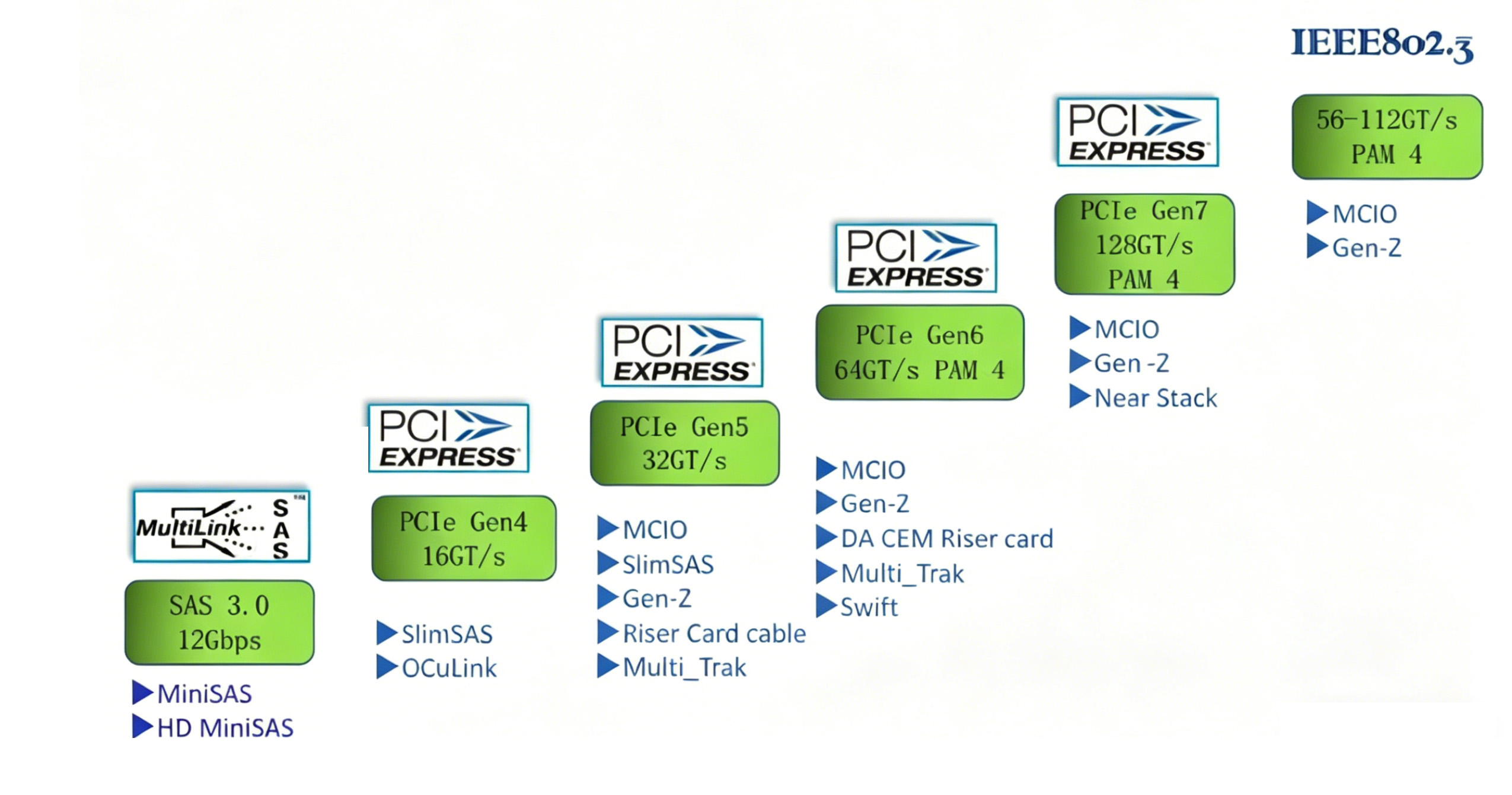

في كل مرة أسمع هذا السؤال، لا بد لي من تفصيله للجميع: الترقية من PCIe 5.0 إلى 6.0 أكثر دراماتيكية من الأجيال السابقة. من 3.0 إلى 4.0 ومن 4.0 إلى 5.0، على الرغم من مضاعفة السرعة أيضًا، ظل المسار الفني كما هو - حيث استخدم كلاهما ترميز NRZ وبنيات معادلة مماثلة. ولكن من 5.0 إلى 6.0، تم استبدال الأساس الفني الكامل للطبقة المادية بالكامل.

لمساعدة الجميع على فهم مدى دقة هذه الترقية، قمت بتجميع مقارنة تفصيلية يسهل فهمها، ولا حاجة إلى الإفراط في التفكير فيها.

أولاً، إليك جدول مقارنات المعلمات الأساسية، حتى تتمكن من رؤية الاختلافات في لمحة سريعة:

البعد المقارنة | بكيي 5.0 | بكيي 6.0 | تغيير النطاق |

معدل البيانات | 32 جي تي / ثانية | 64 جي تي / ثانية | تضاعف |

عرض النطاق الترددي ثنائي الاتجاه x16 | 128 جيجابايت/ثانية | 256 جيجابايت/ثانية | تضاعف |

طريقة الترميز | إن آر زي (PAM2) | بام4 | تنسيق التعديل الجديد |

تردد نيكويست | 16 جيجا هرتز | 16 جيجا هرتز | يبقى دون تغيير |

البتات لكل واجهة مستخدم | 1 بت | 2 بت | تضاعف |

مخطط الترميز | 128ب/130ب | 1b/1b (وضع الطيران) | إعادة الهيكلة بالكامل |

تصحيح الأخطاء إلى الأمام (FEC) | لا أحد | FEC خفيف الوزن | آلية المضافة حديثا |

وحدة التحكم في التدفق | غير قابلة للطيران (حزمة متغيرة) | Flit (ثابت 256 بايت) | الوضع المضافة حديثا |

متطلبات معدل خطأ البت | بير ≥ 1E-12 | فبر ≥ 1E-6 | مؤشر متري جديد |

ميزانية خسارة القناة | 36 ديسيبل @ 16 جيجا هرتز | 32 ديسيبل @ 16 جيجا هرتز | تشديد قليلا |

اختبار Rx لارتفاع العين | 15 مللي فولت | 6 مللي فولت (العين العلوية) | خفضت بشكل ملحوظ |

اختبار عرض العين Rx | 9.375 ملاحظة | 3.125 ملاحظة (العين العلوية) | خفضت بشكل ملحوظ |

مرجع CTLE | 4 أقطاب / 2 أصفار | 6 أقطاب / 3 أصفار | تحسين القدرة على المعادلة |

مرجع DFE | 3 صنابير | 16 صنابير | معززة بشكل كبير |

بعد ذلك، سأقوم بتفصيل ما يكمن وراء كل من هذه الاختلافات واحدًا تلو الآخر، باستخدام لغة واضحة طوال الوقت - بدون مصطلحات غامضة، لذلك أضمن أن الجميع يستطيع فهمها.

1. طريقة التشفير: تحول أساسي من NRZ إلى PAM4

هذا هو الاختلاف الأساسي بين الجيلين، وبمجرد أن تفهم هذا، سيكون من السهل فهم جميع الاختلافات الأخرى.

يستخدم PCIe 5.0 وجميع الإصدارات السابقة تشفير NRZ، المعروف أيضًا باسم تشفير Non-Return-to-Zero، أو PAM2 للاختصار. ببساطة، فإنه يرسل 1 بت لكل وحدة فاصل زمني (بالعامية، "كل وقت إرسال قصير") - إما 0 أو 1. مخطط عين الإشارة (الذي يمكنك اعتباره مخطط "وضوح" الإشارة) هو "عين" كبيرة، وهو أمر بديهي للغاية.

ومع ذلك، يستخدم PCIe 6.0 تشفير PAM4 (تعديل سعة النبض رباعي المستويات) لأول مرة. ميزته هي أنه يمكن إرسال 2 بت لكل وحدة فاصلة، بما يتوافق مع أربعة مستويات: 00، 01، 10، و11. ونتيجة لذلك، يصبح مخطط عين الإشارة ثلاث "عيون" صغيرة مكدسة معًا، وهو ما يعادل تركيب ضعف المعلومات في نفس المقدار من الوقت.

قد يتساءل الكثير من الناس: كيف يمكن لـ PAM4 مضاعفة السرعة دون زيادة التردد؟

الأمر بسيط جدًا في الواقع: تردد Nyquist لـ PCIe 5.0 هو 16 جيجا هرتز (نصف 32 جيجا بايت / ثانية). بعد اعتماد PCIe 6.0 لـ PAM4، على الرغم من مضاعفة السرعة إلى 64GT/s، يظل تردد Nyquist 16 جيجا هرتز — لأنه ينقل بت إضافي واحد لكل فاصل زمني للوحدة. وهذا يعني أن التردد الأساسي للإشارة لا يتغير، وبالتالي فإن متطلبات التردد للوحة الدوائر المطبوعة (PCB) والموصلات لا تزيد بشكل كبير، ويمكن أن تكون مسافة الإرسال مماثلة لمسافة 5.0، دون الحاجة إلى تعديل تصميم نقل الأجهزة.

ولكن ليس هناك وجبة غداء مجانية، فـ PAM4 له أيضًا عيوبه، والتي نحتاج إلى توضيحها:

1. وضوح الإشارة المتدهورة: تم إصلاح سعة الجهد الإجمالي، وكل واحدة من "العيون الصغيرة" الثلاثة لـ PAM4 تبلغ ثلث ارتفاع "العين الكبيرة" لـ NRZ فقط. من الناحية النظرية، فإن وضوح الإشارة (نسبة الإشارة إلى الضوضاء) لـ PAM4 أسوأ بنحو 9.5 ديسيبل من وضوح NRZ، مما يعني ببساطة أنها أكثر عرضة للتداخل.

2. قدرة أضعف على مقاومة التداخل: سواء كان الأمر يتعلق بتداخل مصدر الطاقة، أو الحديث المتبادل بين الإشارات، أو انعكاس الإشارة، فمن المرجح أن تتسبب جميعها في حدوث أخطاء في البت (أخطاء نقل البيانات) في نظام PAM4.

3. اختبار أكثر صعوبة: في الماضي، كانت إشارات الاختبار تتطلب فقط قياس "عين كبيرة" واحدة، ولكن يتعين علينا الآن قياس ثلاث "عيون صغيرة" والانتباه إلى مؤشرات جديدة مثل الخطية (RLM)، مما يزيد بشكل كبير من صعوبة الاختبار وتكلفته.

2. هيكل تدفق البيانات: وضع Flit إلزامي

لا يزال PCIe 5.0 يستخدم الطريقة القديمة: ترميز 128b/130b، والذي يبلغ "الحمل الزائد" حوالي 1.5% (أي أنه عند نقل البيانات، يتعين عليك إرسال محتوى إضافي إضافي غير ذي صلة). كما أنه يدعم حزم TLP (حزم البيانات للإرسال) ذات أحجام مختلفة، وهو وضع يسمى "Non-Flit". كل "حزمة" لها فحص خاص بها (CRC)، وهو ما يعادل "علامة مكافحة التزييف" الحصرية لكل حزمة.

لمطابقة تشفير PAM4 وتقنية تصحيح الأخطاء FEC التي سنناقشها لاحقًا، يجب أن يقوم PCIe 6.0 بتمكين وضع Flit (ببساطة، "حزم البيانات" ذات الحجم الثابت). Flit عبارة عن كتلة بيانات ذات طول ثابت — 256 بايت — وبنيتها الداخلية واضحة، وتنقسم إلى:

- 235 بايت من TLP: البيانات الأساسية التي يجب إرسالها فعليًا

- 6 بايت من DLP: يعادل "تسمية الطبقة الوسطى" للبيانات، وهو مسؤول عن اتصال نقل طبقة الارتباط

- 8 بايت من CRC: رمز فحص يستخدم للتحقق من إرسال البيانات بشكل صحيح

- 6 بايت من FEC: "النسخ الاحتياطي للبيانات" لتصحيح الأخطاء، وهو ما سنشرحه بالتفصيل لاحقًا

قد يتساءل الكثير من الناس: لماذا يتعين علينا استخدام "الحزم" ذات الحجم الثابت؟ الأسباب بسيطة، فقط ثلاث نقاط:

1. ملاءمة لتصحيح خطأ FEC: يتم حساب تصحيح خطأ FEC في كتل ذات طول ثابت، وFlit عبارة عن وحدة معالجة كاملة تمامًا - لا حاجة لتقسيمها، مما يجعلها أكثر كفاءة.

2. تقليل النفقات العامة: تم تحسين النفقات العامة الإضافية القديمة مثل رؤوس المزامنة ورموز الإطارات المميزة. على الرغم من أن الحزم ذات حجم ثابت، إلا أنه تم بالفعل تحسين الاستخدام الإجمالي لعرض النطاق الترددي.

3. معالجة أسهل للأخطاء: أولاً، تقوم FEC بإصلاح الأخطاء الصغيرة القابلة للتصحيح على الفور، ثم تتحقق CRC مرة أخرى. إذا لم يكن من الممكن إصلاحه، فسيتم بدء إعادة الإرسال. العملية واضحة ولا تنطوي على مشاكل ذهابًا وإيابًا.

3. معدل خطأ البت وآلية تصحيح الأخطاء: تمت إضافة وظيفة تصحيح الأخطاء FEC حديثًا

يحتوي PCIe 5.0 على متطلبات صارمة للغاية فيما يتعلق بأخطاء نقل البيانات: يجب ألا يتجاوز معدل خطأ البت من طرف إلى طرف (ببساطة احتمال نقل البيانات غير الصحيحة) 1E-12، مما يعني خطأ 1 بت على الأكثر لكل 1 تريليون بت مرسلة. وهو يعتمد على تقنية معادلة الطبقة المادية بالإضافة إلى إعادة إرسال طبقة الارتباط، دون وجود وظيفة مخصصة لتصحيح الأخطاء.

نظرًا لأن تشفير PAM4 بطبيعته أكثر عرضة لأخطاء البت، يضيف PCIe 6.0 على وجه التحديد تصحيحًا خفيفًا للأخطاء الأمامية (FEC للاختصار؛ بالعامية، "النسخ الاحتياطي لتصحيح الأخطاء" الذي يتم إجراؤه أثناء الإرسال). تحدد المواصفات أيضًا مؤشرًا جديدًا يسمى FBER (معدل خطأ البت الأول)، والذي يتطلب ≥ 1E-6. على الرغم من أن هذا يبدو أكثر مرونة من متطلبات الإصدار 5.0، إلا أنه بمساعدة FEC، تكون القدرة الإجمالية لتصحيح الأخطاء أقوى في الواقع.

كيف يعمل FEC؟ الأمر بسيط: عند إرسال البيانات، يتم حساب 6 بايت من معلومات FEC الزائدة (أي "بيانات النسخ الاحتياطي") لكل رحلة وإرسالها معها. بعد الاستلام، يستخدم جهاز الاستقبال أولاً FEC لإصلاح الأخطاء الصغيرة القابلة للتصحيح على الفور. إذا كان الخطأ كبيرًا جدًا بحيث لا يمكن إصلاحه بواسطة FEC، فإن CRC يكتشفه ويبدأ إعادة الإرسال.

إن مزايا هذه الآلية المكونة من خطوتين "FEC أولاً لتصحيح الخطأ، ثم CRC للتحقق من الخطأ" واضحة بشكل خاص:

- يمكن إصلاح معظم الأخطاء الصغيرة ذات البت الواحد مباشرة عن طريق FEC دون إعادة الإرسال، مما يحافظ على زمن الوصول تحت السيطرة ولا يؤدي إلى إبطاء السرعة الإجمالية.

- احتمالية إعادة الإرسال منخفضة للغاية، ويتم التحكم فيها ضمن 5E-6، ويبلغ استهلاك النطاق الترددي الإضافي حوالي 0.05% فقط، وهو ما لا يؤثر إلا بالكاد على الاستخدام العادي.

- بالمقارنة مع تقنية RS-FEC الخاصة بشبكة Ethernet (زمن الوصول حوالي 100 نانو ثانية)، تتمتع تقنية FEC خفيفة الوزن الخاصة بـ PCIe 6.0 بزمن وصول أقل بكثير ولن تؤثر على التشغيل العادي للأجهزة.

4. معادلة جهاز الاستقبال: ترقية كبيرة في القدرة على تصحيح الأخطاء

أثناء إرسال الإشارات بسرعة عالية، سوف تضعف الإشارات، تمامًا مثلما يصبح الصوت أكثر هدوءًا كلما انتقل أبعد. في هذا الوقت، هناك حاجة إلى تقنية "المعادلة" للتعويض، مما يسمح لجهاز الاستقبال باستقبال الإشارة بوضوح. يحتوي DFE المرجعي لـ PCIe 5.0 (معادلة ردود الفعل على القرار، وهو نوع من تقنيات تصحيح الأخطاء) على 3 نقرات، أي ما يعادل 3 "مساعدين لتصحيح الأخطاء" فقط.

نظرًا لأن إشارات PAM4 أكثر عرضة للتداخل، فإن PCIe 6.0 لديه متطلبات أعلى لقدرة تصحيح الأخطاء. يقفز مرجع DFE إلى 16 نقرة، أي ما يعادل عدة مرات أكثر من "مساعدي تصحيح الأخطاء". تم أيضًا تحسين قدرة معالجة الإشارات الرقمية لجهاز الاستقبال بشكل كبير، وأصبحت أكثر قدرة على التخلص من "تداخل الذيل" (التداخل الإضافي المتبقي بعد إرسال الإشارة).

بالإضافة إلى ذلك، تمت أيضًا ترقية CTLE (المعادلة الخطية للوقت المستمر)، من 4 أقطاب/2 أصفار إلى 6 أقطاب/3 أصفار، مع قدرة أقوى على التعويض عن توهين الإشارة.

قد يتساءل الكثير من الناس: لماذا نحتاج إلى الكثير من "مساعدي تصحيح الأخطاء" (الصنابير)؟ لأن "العيون الصغيرة" الثلاثة لـ PAM4 لها متطلبات معادلة مختلفة - خاصة العيون العلوية والسفلية، والتي تكون أكثر عرضة للتداخل غير الخطي. فقط DFE الأقوى يمكنه ضبط "العيون الصغيرة" الثلاث لتكون واضحة، مما يضمن إمكانية استقبال الإشارة بشكل طبيعي.

5. سلامة الإشارة: متطلبات أكثر صرامة، لا مجال للتسوية

يتضح من جدول المعلمات أعلاه أن متطلبات اختبار PCIe 6.0 أكثر صرامة من متطلبات اختبار 5.0. دعونا نحلل بالضبط مدى صرامتهم، واحدًا تلو الآخر:

- ارتفاع عين اختبار Rx: تم تقليله من 15 مللي فولت في 5.0 إلى 6 مللي فولت في 6.0 (فقط للعين العلوية)، وهو ما يعادل أكثر من ضعف "معيار الوضوح" للإشارات.

- عرض عين اختبار Rx: تم تقليله من 9.375ps في 5.0 إلى 3.125ps في 6.0 (لا يزال للعين العلوية)، مما يزيد أيضًا بشكل كبير من متطلبات دقة الوقت.

- متطلبات ارتعاش الساعة المرجعية: تم تشديدها من ≥0.25ps RMS إلى ≥0.15ps RMS. ببساطة، متطلبات استقرار الساعة أعلى، ولا يوجد مجال للانحراف.

- ميزانية فقدان القناة: تم تخفيضها من 36 ديسيبل عند 16 جيجا هرتز إلى 32 ديسيبل عند 16 جيجا هرتز، مما يعني أن توهين الإشارة أثناء الإرسال لا يمكن أن يكون كبيرًا جدًا، وأن متطلبات الأجهزة أكثر صرامة.

وهذا يعني أن التصميمات التي كانت "جيدة بما فيه الكفاية" في عصر PCIe 5.0 ستكون عديمة الفائدة تمامًا في عصر 6.0. يجب التحكم بدقة في كل ثقب في لوحة PCB، وكل ملليمتر من الأسلاك، وكل موصل - ولا مجال للإهمال.

هناك العديد من التحديات الرئيسية هنا، والتي سأسلط الضوء عليها للجميع:

1. مادة ثنائي الفينيل متعدد الكلور: يجب استخدام مواد ذات خسارة منخفضة للغاية، مثل MEGTRON 7 وRO4835. مواد FR-4 العادية التي نستخدمها عادةً لا يمكنها تحمل توهين الإشارة عند 32 جيجا هرتز وستتسبب بسهولة في حدوث أخطاء في نقل البيانات إذا تم استخدامها.

2. الموصلات: أصبحت الموصلات المثبتة على السطح قياسية، ويجب أن تكون عملية الضغط دقيقة للغاية. سيؤثر الانحراف الطفيف على الإشارة ويسبب نقلًا غير مستقر.

3. استقرار مصدر الطاقة: PAM4 حساس جدًا لتداخل مصدر الطاقة. لا يمكن لتصميم مصدر الطاقة السابق تلبية المتطلبات على الإطلاق، لذلك يجب إعادة تصميم شبكة توزيع الطاقة (PDN) لضمان إمدادات طاقة مستقرة.

4. التحكم في الحديث المتبادل: التباعد بين الأزواج التفاضلية، وممرات الأرض المحمية - لا يمكن حذف كل التفاصيل. سيؤدي الإشراف البسيط إلى حدوث تداخل بين الإشارات ويؤثر على جودة الإرسال.

6. الآفاق التجارية: على مستوى المؤسسات أولاً، على مستوى المستهلك للانتظار

من منظور التطبيق العملي، فإن وضع هذين الجيلين من المنتجات مختلف تمامًا. دعونا نقسمها إلى فئتين، حتى يتمكن الجميع من فهمها في لمحة واحدة.

يحظى PCIe 5.0 الآن بشعبية كبيرة في خوادم الذكاء الاصطناعي ومراكز البيانات. سواء كانت بطاقات الرسومات من سلسلة NVIDIA's RTX 50، أو بطاقات الرسومات من سلسلة AMD's RX 9000، أو محركات الأقراص ذات الحالة الصلبة (SSD) على مستوى المؤسسات، فكلها تدعم PCIe 5.0 ويتم استخدامها على نطاق واسع.

في المقابل، يعتبر تسويق PCIe 6.0 بطيئًا نسبيًا. على الرغم من إصدار المواصفات في أوائل عام 2022، فإن الأجهزة الفعلية المتاحة لن تصل إلى السوق حتى عام 2026. وهناك ثلاثة أسباب واقعية رئيسية لذلك:

1. التكلفة العالية: تبلغ تكلفة إزالة الشريط لوحدة التحكم PCIe 6.0 حوالي 20-35 مليون دولار أمريكي، أي ضعف تكلفة 5.0. يتحمل المصنعون تكاليف استثمار عالية ولن يتمكنوا من إدخالها بسهولة في الإنتاج الضخم.

2. عتبة تقنية عالية: يتطلب تصميم PAM4 والتحقق من المنتج واختباره سلسلة أدوات جديدة تمامًا. العديد من الشركات المصنعة لم تتقن هذه التكنولوجيا بعد ولا يمكنها إنتاج منتجات مؤهلة في وقت قصير.

3. الطلبات المتباينة: تحتاج مراكز بيانات الذكاء الاصطناعي والحوسبة عالية الأداء (HPC) حقًا إلى النطاق الترددي العالي لـ PCIe 6.0 لنقل البيانات بشكل أسرع وكفاءة أعلى. ومع ذلك، بالنسبة لأجهزة الكمبيوتر الاستهلاكية العادية ووحدات التحكم في الألعاب، لا يوجد أي طلب تقريبًا على 6.0، حيث أن محركات أقراص PCIe 5.0 SSD الحالية سريعة جدًا بالفعل بحيث لا يمكن للمستخدمين ملاحظة الفرق؛ السرعات الأعلى ليست ضرورية.

وفقًا لتوقعات الصناعة، قد لا يحظى PCIe 6.0 بشعبية في السوق الاستهلاكية إلا بعد عام 2030. ولكن في مجال المؤسسات، وخاصة خوادم الذكاء الاصطناعي، سيبدأ النشر على نطاق واسع في 2026-2027، ليهبط أولاً في المجالات المهنية.

ملخص: الفرق الجوهري بين الجيلين

العودة إلى السؤال الأصلي: ما الفرق الحقيقي بين PCIe 5.0 و6.0؟

لتلخيص الأمر بلغة واضحة: 5.0 هو سقف عصر تشفير NRZ، مما يدفع التكنولوجيا القديمة إلى أقصى حدودها؛ في حين أن الإصدار 6.0 هو نقطة البداية لعصر التشفير PAM4، مما يفتح طريقًا تقنيًا جديدًا تمامًا.

البعد | بكيي 5.0 | بكيي 6.0 |

الجوهر الفني | دفع ترميز NRZ إلى الحد الأقصى | التحول إلى مسار التشفير PAM4 الجديد |

خصائص الإشارة | "عين واحدة كبيرة"، إشارة واضحة | ثلاث "عيون صغيرة" عرضة للتدخل |

آلية تصحيح الخطأ | يعتمد على فحص CRC؛ يعيد الإرسال إذا كان هناك خطأ | تصحيح FEC أولاً؛ يعيد الإرسال إذا لم يكن من الممكن إصلاحه |

صعوبة التصميم | عالية، ولكن يمكن التحكم فيها | عالية للغاية، مع عتبة فنية عالية |

متطلبات الاختبار | حازم؛ فقط اتبع المعايير | صارمة للغاية؛ لا مجال للأخطاء التفصيلية |

سيناريوهات التطبيق | مشهور في خوادم الذكاء الاصطناعي؛ يمكن استخدامها أيضًا على مستوى المستهلك | مستوى المؤسسات بدأ للتو؛ المستهلك الصف للانتظار |

بالنسبة للمهندسين، فإن العمل على PCIe 5.0 يختبر قدرتهم على تحسين التقنيات القديمة وتحسينها؛ يعمل العمل على PCIe 6.0 على اختبار قدرتهم على تعلم تقنيات جديدة والتكيف مع الطرق الجديدة. بالنسبة للصناعة بأكملها، تعد 5.0 تقنية ناضجة وقابلة للاستخدام وموثوقة اليوم، في حين أن 6.0 هو الاتجاه المستقبلي - ولكن هذا المستقبل سيأتي أولاً من مراكز البيانات، ثم يشق طريقه ببطء إلى حياة المستخدمين العاديين.

|(ملاحظة: قد تكون أجزاء من المستندمنظمة العفو الدوليةيولد)