Hersteller von hochwertigem Datenkabel

Hersteller von hochwertigem Datenkabel

Epigraph: Von 32GT/s auf 64GT/s scheint es nur eine Verdoppelung der Geschwindigkeit zu sein, aber dahinter steckt eine völlige Transformation der technischen Route.

Einleitung: Mehr als nur die Verdoppelung der Geschwindigkeit

Nachdem ich so viele Jahre in der KI-Server- und Rechenzentrumsbranche gearbeitet habe, wird mir am häufigsten die Frage gestellt: Was ist der wirkliche Unterschied zwischen PCIe 5.0 und 6.0? Verdoppelt sich dadurch nicht einfach die Geschwindigkeit?

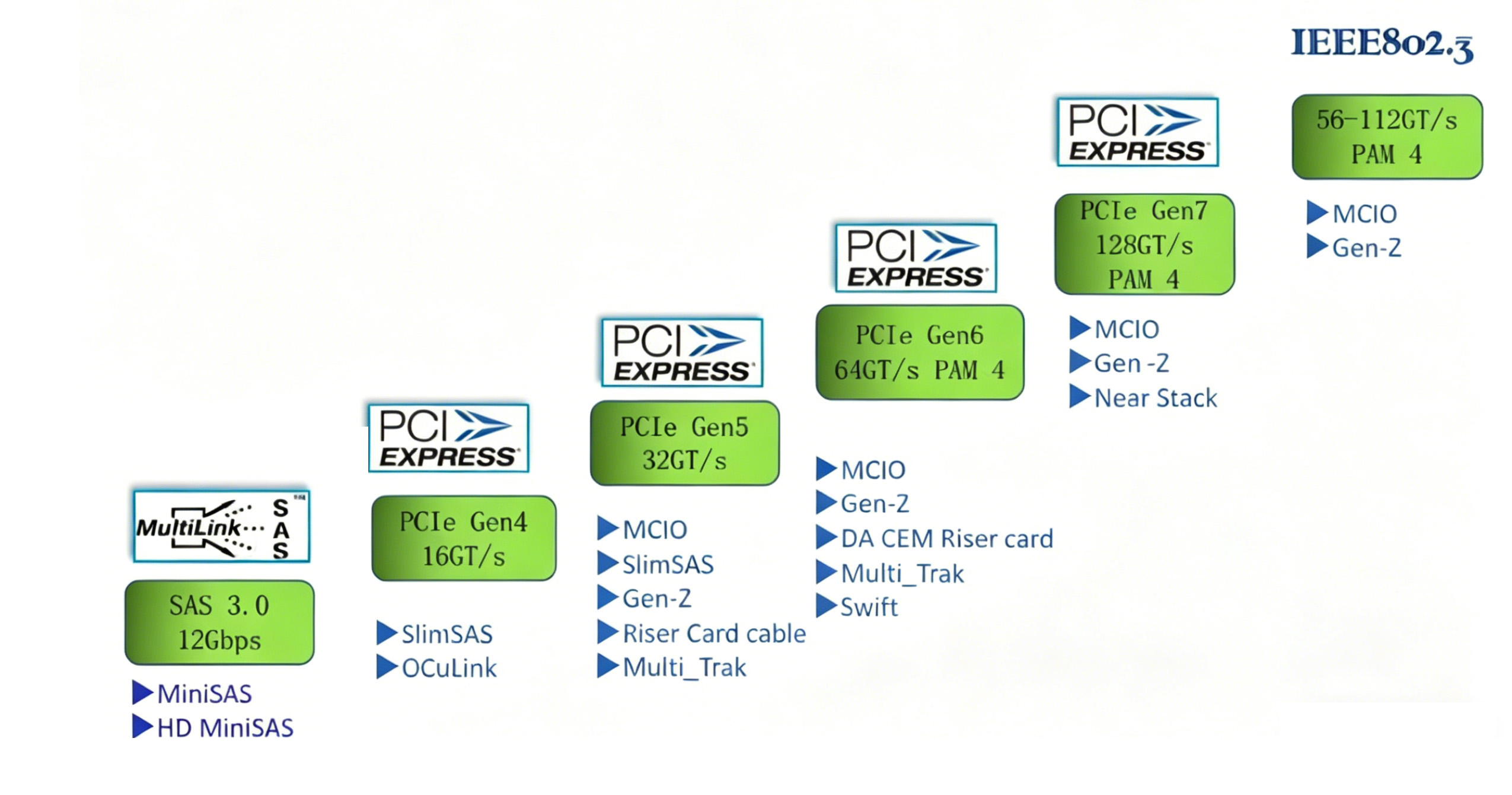

Jedes Mal, wenn ich diese Frage höre, muss ich sie für alle aufschlüsseln: Das Upgrade von PCIe 5.0 auf 6.0 ist viel dramatischer als bei den vorherigen Generationen. Von 3.0 auf 4.0 und von 4.0 auf 5.0 verdoppelte sich zwar auch die Geschwindigkeit, der technische Weg blieb jedoch im Wesentlichen derselbe – beide verwendeten NRZ-Kodierung und ähnliche Entzerrungsarchitekturen. Von 5.0 auf 6.0 wurde jedoch die gesamte technische Grundlage der physikalischen Schicht vollständig ersetzt.

Damit jeder versteht, wie gründlich dieses Upgrade ist, habe ich einen detaillierten Vergleich zusammengestellt, der leicht zu verstehen ist und keinen Grund zum Nachdenken bietet.

Hier ist zunächst eine Tabelle mit Kernparametervergleichen, damit Sie die Unterschiede auf einen Blick erkennen können:

Vergleichsdimension | PCIe 5.0 | PCIe 6.0 | Bereich ändern |

Datenrate | 32 GT/s | 64 GT/s | Verdoppelt |

x16 Bidirektionale Bandbreite | 128 GB/s | 256 GB/s | Verdoppelt |

Kodierungsmethode | NRZ (PAM2) | PAM4 | Neues Modulationsformat |

Nyquist-Frequenz | 16 GHz | 16 GHz | Bleibt unverändert |

Bits pro Benutzeroberfläche | 1 Bit | 2 Bit | Verdoppelt |

Kodierungsschema | 128b/130b | 1b/1b (Flit-Modus) | Komplett neu strukturiert |

Vorwärtsfehlerkorrektur (FEC) | Keiner | Leichtes FEC | Neu hinzugefügter Mechanismus |

Durchflusskontrolleinheit | Non-Flit (Variables Paket) | Flit (Feste 256 Bytes) | Neu hinzugefügter Modus |

Anforderung an die Bitfehlerrate | BER ≤ 1E-12 | FBER ≤ 1E-6 | Neuer metrischer Indikator |

Kanalverlustbudget | 36 dB bei 16 GHz | 32 dB bei 16 GHz | Leicht verschärft |

Rx-Test der Augenhöhe | 15 mV | 6 mV (oberes Auge) | Deutlich reduziert |

Rx-Test-Augenbreite | 9.375 Ps | 3,125 ps (Oberes Auge) | Deutlich reduziert |

Referenz CTLE | 4 Pole/2 Nullen | 6 Pole/3 Nullen | Verbesserte Ausgleichsfähigkeit |

Referenz-DFE | 3 Fingertipps | 16 Wasserhähne | Stark verbessert |

Als Nächstes werde ich nacheinander aufschlüsseln, was sich hinter jedem dieser Unterschiede verbirgt, und dabei stets eine klare Sprache verwenden – keinen obskuren Jargon, sodass ich garantiere, dass jeder ihn verstehen kann.

1. Kodierungsmethode: Ein grundlegender Wechsel von NRZ zu PAM4

Dies ist der Kernunterschied zwischen den beiden Generationen, und sobald Sie dies verstanden haben, werden alle anderen Unterschiede leicht zu verstehen sein.

PCIe 5.0 und alle Vorgängerversionen verwenden die NRZ-Kodierung, auch bekannt als Non-Return-to-Zero-Kodierung, kurz PAM2. Einfach ausgedrückt sendet es 1 Bit pro Intervalleinheit (umgangssprachlich „jede kurze Übertragungszeit“) – entweder 0 oder 1. Das Signalaugendiagramm (das Sie sich als „Klarheitsdiagramm“ des Signals vorstellen können) ist ein großes „Auge“, das sehr intuitiv ist.

PCIe 6.0 nutzt jedoch erstmals die PAM4-Kodierung (Four-Level Pulse Amplitude Modulation). Sein Vorteil besteht darin, dass es 2 Bits pro Einheitsintervall senden kann, was den vier Ebenen 00, 01, 10 und 11 entspricht. Dadurch wird das Signalaugendiagramm zu drei kleinen übereinander gestapelten „Augen“, was dem Anpassen doppelt so vieler Informationen in der gleichen Zeit entspricht.

Viele Leute fragen sich vielleicht: Wie kann PAM4 die Geschwindigkeit verdoppeln, ohne die Frequenz zu erhöhen?

Eigentlich ist es ganz einfach: Die Nyquist-Frequenz von PCIe 5.0 beträgt 16 GHz (die Hälfte von 32 GT/s). Nachdem PCIe 6.0 PAM4 übernommen hat, verdoppelt sich die Geschwindigkeit zwar auf 64 GT/s, die Nyquist-Frequenz bleibt jedoch 16 GHz, da 1 zusätzliches Bit pro Intervalleinheit übertragen wird. Dies bedeutet, dass sich die Grundfrequenz des Signals nicht ändert, sodass die Frequenzanforderungen für die Leiterplatte (PCB) und die Anschlüsse nicht wesentlich steigen und die Übertragungsentfernung der von 5.0 ähneln kann, ohne dass das Hardware-Übertragungsdesign geändert werden muss.

Aber es gibt kein kostenloses Mittagessen – PAM4 hat auch seine Mängel, die wir deutlich machen müssen:

1. Verschlechterte Signalklarheit: Die Gesamtspannungsamplitude ist fest und jedes der drei „kleinen Augen“ von PAM4 ist nur ein Drittel so hoch wie das „große Auge“ von NRZ. Theoretisch ist die Signalklarheit (Signal-Rausch-Verhältnis) von PAM4 etwa 9,5 dB schlechter als die von NRZ, was einfach bedeutet, dass es anfälliger für Störungen ist.

2. Schwächere Anti-Interferenz-Fähigkeit: Ob es sich um Störungen der Stromversorgung, Übersprechen zwischen Signalen oder Signalreflexion handelt, alle verursachen mit größerer Wahrscheinlichkeit Bitfehler (Datenübertragungsfehler) in einem PAM4-System.

3. Aufwändigeres Testen: Früher erforderte das Testen von Signalen nur die Messung eines „großen Auges“, aber jetzt müssen wir drei „kleine Augen“ messen und auf neue Indikatoren wie Linearität (RLM) achten, was die Schwierigkeit und die Kosten des Testens erheblich erhöht.

2. Datenstromstruktur: Der Flit-Modus ist obligatorisch

PCIe 5.0 verwendet immer noch die alte Methode: 128b/130b-Kodierung, die einen „Overhead“ von etwa 1,5 % hat (was bedeutet, dass Sie bei der Datenübertragung etwas mehr irrelevante Hilfsinhalte senden müssen). Es unterstützt auch TLP-Pakete (Datenpakete zur Übertragung) unterschiedlicher Größe, ein Modus namens „Non-Flit“. Jedes „Paket“ verfügt über eine eigene Prüfung (CRC), die einem exklusiven „Anti-Fälschungs-Label“ für jedes Paket entspricht.

Um mit der PAM4-Kodierung und der FEC-Fehlerkorrekturtechnologie übereinzustimmen, die wir später besprechen werden, muss PCIe 6.0 den Flit-Modus (einfach ausgedrückt: „Datenpakete“ mit fester Größe) aktivieren. Ein Flit ist ein Datenblock fester Länge – 256 Bytes – und seine interne Struktur ist klar und gliedert sich in:

- 235 Byte TLP: Die Kerndaten, die tatsächlich übertragen werden müssen

- 6 Byte DLP: Entspricht einem „Middle-Layer-Label“ für die Daten, verantwortlich für die Verbindungsschicht-Übertragungsverbindung

- 8 Byte CRC: Ein Prüfcode, mit dem überprüft wird, ob die Daten korrekt übertragen wurden

- 6 Bytes FEC: „Backup-Daten“ zur Fehlerkorrektur, die wir später im Detail erläutern

Viele Leute fragen sich vielleicht: Warum müssen wir „Pakete“ mit fester Größe verwenden? Die Gründe sind einfach, nur drei Punkte:

1. Praktisch für die FEC-Fehlerkorrektur: Die FEC-Fehlerkorrektur wird in Blöcken fester Länge berechnet, und ein Flit ist genau eine vollständige Verarbeitungseinheit – es ist nicht nötig, sie aufzuteilen, was sie effizienter macht.

2. Reduzierter Overhead: Der alte zusätzliche Overhead wie Synchronisierungsheader und Framing-Tokens wurde optimiert. Obwohl die Pakete eine feste Größe haben, wird die Gesamtbandbreitennutzung tatsächlich verbessert.

3. Einfachere Fehlerbehandlung: Zuerst behebt FEC kleine korrigierbare Fehler vor Ort, dann prüft CRC erneut. Wenn das Problem nicht behoben werden kann, wird eine erneute Übertragung eingeleitet. Der Prozess ist klar und erfordert kein hin und her.

3. Bitfehlerrate und Fehlerkorrekturmechanismus: Neu hinzugefügte FEC-Fehlerkorrekturfunktion

PCIe 5.0 stellt sehr strenge Anforderungen an Datenübertragungsfehler: Die Ende-zu-Ende-Bitfehlerrate (einfach die Wahrscheinlichkeit einer fehlerhaften Datenübertragung) darf 1E-12 nicht überschreiten, d. h. höchstens 1 Bitfehler pro 1 Billion übertragener Bits. Es basiert auf der Entzerrungstechnologie der physikalischen Schicht und der erneuten Übertragung der Verbindungsschicht und verfügt über keine spezielle Fehlerkorrekturfunktion.

Da die PAM4-Kodierung von Natur aus anfälliger für Bitfehler ist, fügt PCIe 6.0 speziell eine leichte Vorwärtsfehlerkorrektur (kurz FEC; umgangssprachlich „Fehlerkorrektur-Backup“, das während der Übertragung durchgeführt wird) hinzu. Die Spezifikation definiert außerdem einen neuen Indikator namens FBER (First Bit Error Rate), der ≤ 1E-6 erfordert. Obwohl dies lockerer zu sein scheint als die Anforderungen von 5.0, ist die allgemeine Fehlerkorrekturfähigkeit mit FEC-Unterstützung tatsächlich stärker.

Wie funktioniert FEC? Es ist ganz einfach: Beim Senden von Daten werden für jedes Flit 6 Byte FEC-redundante Informationen (also „Backup-Daten“) berechnet und mitgesendet. Nach dem Empfang nutzt der Empfänger zunächst FEC, um kleine korrigierbare Fehler vor Ort zu beheben. Wenn der Fehler zu groß ist, als dass FEC ihn beheben könnte, erkennt CRC ihn und leitet eine erneute Übertragung ein.

Die Vorteile dieses zweistufigen Mechanismus „zuerst FEC zur Fehlerkorrektur, dann CRC zur Fehlerverifizierung“ liegen besonders auf der Hand:

- Die meisten kleinen Einzelbitfehler können direkt durch FEC ohne erneute Übertragung behoben werden, wodurch die Latenz unter Kontrolle bleibt und die Gesamtgeschwindigkeit nicht verlangsamt wird.

- Die Wahrscheinlichkeit einer erneuten Übertragung ist sehr gering und wird innerhalb von 5E-6 kontrolliert, und der zusätzliche Bandbreitenverbrauch beträgt nur etwa 0,05 %, was die normale Nutzung kaum beeinträchtigt.

- Im Vergleich zu RS-FEC von Ethernet (Latenz von etwa 100 Nanosekunden) hat das leichte FEC von PCIe 6.0 eine viel geringere Latenz und beeinträchtigt den normalen Betrieb von Geräten nicht.

4. Empfängerausgleich: Erhebliche Verbesserung der Fehlerkorrekturfähigkeit

Bei der Hochgeschwindigkeits-Signalübertragung werden die Signale gedämpft – genauso wie der Ton immer leiser wird, je weiter er sich ausbreitet. Zu diesem Zeitpunkt ist zum Ausgleich eine „Entzerrungs“-Technologie erforderlich, die es dem Empfänger ermöglicht, das Signal klar zu empfangen. Das Referenz-DFE (Decision Feedback Equalization, eine Art Fehlerkorrekturtechnologie) von PCIe 5.0 verfügt über drei Abgriffe, was nur drei „Fehlerkorrekturassistenten“ entspricht.

Da PAM4-Signale anfälliger für Störungen sind, stellt PCIe 6.0 höhere Anforderungen an die Fehlerkorrekturfähigkeit. Das Referenz-DFE springt auf 16 Taps – was einem Vielfachen von „Fehlerkorrekturassistenten“ entspricht. Auch die Fähigkeit des Empfängers zur digitalen Signalverarbeitung wurde deutlich verbessert, so dass „Tail Interference“ (die zusätzlichen Interferenzen, die nach der Signalübertragung zurückbleiben) besser eliminiert werden können.

Darüber hinaus wurde auch CTLE (Continuous Time Linear Equalization) verbessert, von 4 Polen/2 Nullen auf 6 Pole/3 Nullen, mit stärkerer Fähigkeit, Signaldämpfung zu kompensieren.

Viele fragen sich vielleicht: Warum brauchen wir so viele „Fehlerkorrekturassistenten“ (Taps)? Denn die drei „kleinen Augen“ von PAM4 haben unterschiedliche Ausgleichsanforderungen – insbesondere die oberen und unteren Augen, die anfälliger für nichtlineare Interferenzen sind. Nur ein stärkeres DFE kann alle drei „kleinen Augen“ so einstellen, dass sie klar sind, sodass das Signal normal empfangen werden kann.

5. Signalintegrität: Strengere Anforderungen, kein Raum für Kompromisse

Aus der obigen Parametertabelle geht klar hervor, dass die Testanforderungen von PCIe 6.0 viel strenger sind als die von 5.0. Lassen Sie uns einzeln aufschlüsseln, wie streng sie sind:

- Rx-Test-Augenhöhe: Reduziert von 15 mV in 5,0 auf 6 mV in 6,0 (nur für das obere Auge), was mehr als einer Verdoppelung des „Klarheitsstandards“ für Signale entspricht.

- Rx-Test-Augenbreite: Reduziert von 9,375 ps in 5.0 auf 3,125 ps in 6.0 (immer noch für das obere Auge), was auch die Anforderungen an die Zeitgenauigkeit erheblich erhöht.

- Referenztakt-Jitter-Anforderung: Von ≤ 0,25 ps RMS auf ≤ 0,15 ps RMS verschärft. Einfach ausgedrückt sind die Anforderungen an die Taktstabilität höher und es besteht kein Spielraum für Abweichungen.

- Kanalverlustbudget: Reduziert von 36 dB bei 16 GHz auf 32 dB bei 16 GHz, was bedeutet, dass die Signaldämpfung während der Übertragung nicht zu groß sein darf und die Hardwareanforderungen strenger sind.

Das bedeutet, dass Designs, die in der PCIe 5.0-Ära „gut genug“ waren, in der 6.0-Ära völlig nutzlos sein werden. Jedes Loch auf der Leiterplatte, jeder Millimeter der Verkabelung und jeder Stecker müssen präzise kontrolliert werden – kein Platz für Nachlässigkeit.

Hier gibt es mehrere zentrale Herausforderungen, die ich für alle hervorheben möchte:

1. PCB-Material: Es müssen extrem verlustarme Materialien wie MEGTRON 7 und RO4835 verwendet werden. Gewöhnliche FR-4-Materialien, die wir normalerweise verwenden, können der Signaldämpfung bei 32 GHz nicht standhalten und führen bei Verwendung leicht zu Datenübertragungsfehlern.

2. Steckverbinder: Oberflächenmontierte Steckverbinder sind zum Standard geworden und der Einpressvorgang muss äußerst präzise sein. Eine geringfügige Abweichung beeinträchtigt das Signal und führt zu einer instabilen Übertragung.

3. Stabilität der Stromversorgung: PAM4 reagiert sehr empfindlich auf Störungen der Stromversorgung. Das bisherige Stromversorgungsdesign kann den Anforderungen überhaupt nicht gerecht werden, daher muss das Stromverteilungsnetz (PDN) neu gestaltet werden, um eine stabile Stromversorgung zu gewährleisten.

4. Crosstalk-Kontrolle: Der Abstand der Differentialpaare, die Durchkontaktierungen der abgeschirmten Masse – jedes Detail kann nicht weggelassen werden. Ein geringfügiges Versehen führt zu Übersprechen zwischen Signalen und beeinträchtigt die Übertragungsqualität.

6. Kommerzielle Aussichten: zuerst auf Unternehmensniveau, dann auf Verbraucherniveau

Aus praktischer Anwendungsperspektive ist die Positionierung dieser beiden Produktgenerationen sehr unterschiedlich. Teilen wir es in zwei Kategorien auf, damit jeder es auf einen Blick verstehen kann.

PCIe 5.0 erfreut sich mittlerweile bei KI-Servern und Rechenzentren großer Beliebtheit. Ganz gleich, ob es sich um die Grafikkarten der RTX 50-Serie von NVIDIA, die Grafikkarten der RX 9000-Serie von AMD oder um Solid-State-Laufwerke (SSDs) der Enterprise-Klasse handelt, alle unterstützen PCIe 5.0 und sind weit verbreitet.

Im Gegensatz dazu verläuft die Kommerzialisierung von PCIe 6.0 relativ langsam. Obwohl die Spezifikation Anfang 2022 veröffentlicht wurde, werden tatsächlich verfügbare Geräte erst 2026 auf den Markt kommen. Dafür gibt es vor allem drei realistische Gründe:

1. Hohe Kosten: Die Tape-Out-Kosten eines PCIe 6.0-Controllers betragen etwa 20–35 Millionen US-Dollar, doppelt so viel wie bei 5.0. Die Investitionskosten der Hersteller sind hoch und sie werden es nicht ohne weiteres in die Massenproduktion bringen.

2. Hoher technischer Schwellenwert: PAM4-Design, Produktverifizierung und Tests erfordern alle eine brandneue Toolchain. Viele Hersteller beherrschen diese Technologie noch nicht und können nicht in kurzer Zeit qualifizierte Produkte herstellen.

3. Unterschiedliche Anforderungen: Rechenzentren für KI und Hochleistungsrechnen (HPC) benötigen unbedingt die hohe Bandbreite von PCIe 6.0 für eine schnellere Datenübertragung und höhere Effizienz. Für normale Consumer-Computer und Spielekonsolen besteht jedoch fast keine Nachfrage nach 6.0 – aktuelle PCIe 5.0-SSDs sind bereits so schnell, dass Benutzer den Unterschied nicht bemerken; höhere Geschwindigkeiten sind nicht erforderlich.

Branchenprognosen zufolge wird PCIe 6.0 auf dem Verbrauchermarkt möglicherweise erst nach 2030 beliebt sein. Aber im Unternehmensbereich, insbesondere bei KI-Servern, wird der groß angelegte Einsatz in den Jahren 2026–2027 beginnen und zunächst in professionellen Bereichen landen.

Zusammenfassung: Der wesentliche Unterschied zwischen den beiden Generationen

Zurück zur ursprünglichen Frage: Was ist der wirkliche Unterschied zwischen PCIe 5.0 und 6.0?

Um es im Klartext zusammenzufassen: 5.0 ist der Höhepunkt der NRZ-Kodierungsära und bringt alte Technologie an ihre Grenzen; während 6.0 der Ausgangspunkt der PAM4-Kodierungsära ist und einen völlig neuen technischen Weg eröffnet.

Dimension | PCIe 5.0 | PCIe 6.0 |

Technische Essenz | Die NRZ-Kodierung wird an ihre Grenzen gebracht | Umstellung auf die neue PAM4-Codierungsspur |

Signaleigenschaften | Ein „großes Auge“, klares Signal | Drei „kleine Augen“, anfällig für Störungen |

Fehlerkorrekturmechanismus | Verlässt sich auf CRC-Prüfung; Wird erneut gesendet, wenn ein Fehler auftritt | FEC korrigiert zuerst; Wird erneut übertragen, wenn das Problem nicht behoben werden kann |

Designschwierigkeit | Hoch, aber beherrschbar | Extrem hoch, mit hoher technischer Schwelle |

Testanforderungen | Strikt; Befolgen Sie einfach die Standards | Extrem streng; Kein Platz für Detailfehler |

Anwendungsszenarien | Beliebt bei KI-Servern; auch für den Consumer-Bereich geeignet | Die Enterprise-Klasse steht gerade erst am Anfang; Verbraucherqualität zum Warten |

Für Ingenieure stellt die Arbeit an PCIe 5.0 ihre Fähigkeit auf die Probe, alte Technologien zu verfeinern und zu perfektionieren; Die Arbeit an PCIe 6.0 testet ihre Fähigkeit, neue Technologien zu erlernen und sich an neue Routen anzupassen. Für die gesamte Branche ist 5.0 eine ausgereifte Technologie, die heute nutzbar und zuverlässig ist, während 6.0 die zukünftige Richtung darstellt – aber diese Zukunft wird zunächst aus Rechenzentren kommen und dann langsam ihren Weg in das Leben normaler Benutzer finden.

|(Hinweis: Teile des Dokuments können seinKIerzeugen)