Fabrikant van hoogwaardige gegevenskabel

Fabrikant van hoogwaardige gegevenskabel

Epigrafie: Van 32GT/s naar 64GT/s lijkt het misschien slechts een verdubbeling van de snelheid, maar daarachter gaat een complete transformatie van de technische route schuil.

Inleiding: meer dan alleen een verdubbeling van de snelheid

Na zoveel jaren in de AI-server- en datacenterindustrie te hebben gewerkt, is de vraag die mij het vaakst wordt gesteld: wat is het echte verschil tussen PCIe 5.0 en 6.0? Is het niet gewoon een verdubbeling van de snelheid?

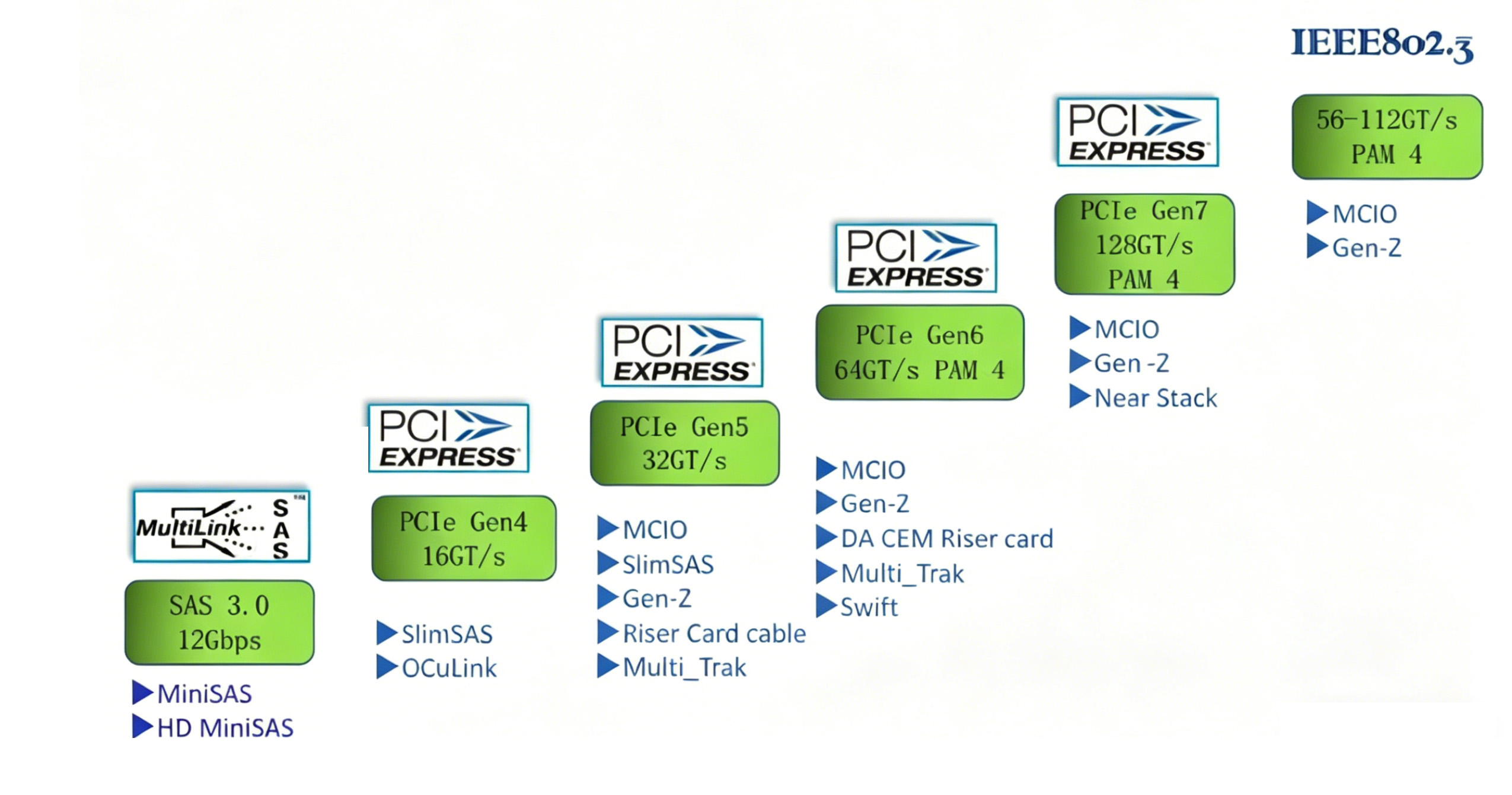

Elke keer dat ik deze vraag hoor, moet ik hem voor iedereen opsplitsen: de upgrade van PCIe 5.0 naar 6.0 is veel dramatischer dan de vorige generaties. Van 3.0 naar 4.0 en van 4.0 naar 5.0, hoewel de snelheid ook verdubbelde, bleef de technische route in wezen hetzelfde: beide gebruikten NRZ-codering en vergelijkbare egalisatie-architecturen. Maar van 5.0 naar 6.0 is de gehele technische basis van de fysieke laag volledig vervangen.

Om iedereen te helpen begrijpen hoe grondig deze upgrade is, heb ik een gedetailleerde vergelijking samengesteld die gemakkelijk te begrijpen is, je hoeft er niet over na te denken.

Ten eerste is hier een tabel met vergelijkingen van kernparameters, zodat u de verschillen in één oogopslag kunt zien:

Vergelijkingsdimensie | PCIe 5.0 | PCIe 6.0 | Wijzig bereik |

Gegevenssnelheid | 32 GT/s | 64 GT/s | Verdubbeld |

x16 Bidirectionele bandbreedte | 128 GB/sec | 256 GB/sec | Verdubbeld |

Coderingsmethode | NRZ (PAM2) | PAM4 | Nieuw modulatieformaat |

Nyquist-frequentie | 16 GHz | 16 GHz | Blijft onveranderd |

Bits per gebruikersinterface | 1 beetje | 2 bits | Verdubbeld |

Coderingsschema | 128b/130b | 1b/1b (Flit-modus) | Volledig geherstructureerd |

Voorwaartse foutcorrectie (FEC) | Geen | Lichtgewicht FEC | Nieuw toegevoegd mechanisme |

Stroomregeleenheid | Non-Flit (variabel pakket) | Flit (vast 256 bytes) | Nieuw toegevoegde modus |

Vereiste bitfoutfrequentie | BER ≤ 1E-12 | FBER ≤ 1E-6 | Nieuwe metrische indicator |

Kanaalverliesbudget | 36 dB @ 16 GHz | 32dB @ 16GHz | Iets strakker |

Rx-test ooghoogte | 15 mV | 6 mV (bovenste oog) | Aanzienlijk verminderd |

Rx-test oogbreedte | 9.375 st | 3.125 ps (bovenste oog) | Aanzienlijk verminderd |

Referentie CTLE | 4 Polen/2 nullen | 6 Polen/3 nullen | Verbeterde egalisatiemogelijkheden |

Referentie DFE | 3 tikken | 16 kranen | Sterk verbeterd |

Vervolgens zal ik één voor één uiteenzetten wat er achter elk van deze verschillen zit, waarbij ik overal duidelijke taal gebruik – geen obscuur jargon, dus ik garandeer dat iedereen het kan begrijpen.

1. Codeermethode: een fundamentele verschuiving van NRZ naar PAM4

Dit is het kernverschil tussen de twee generaties, en als je dit eenmaal begrijpt, zullen alle andere verschillen gemakkelijk te begrijpen zijn.

PCIe 5.0 en alle eerdere versies gebruiken NRZ-codering, ook wel bekend als Non-Return-to-Zero-codering, of kortweg PAM2. Simpel gezegd verzendt het 1 bit per eenheidsinterval (in de volksmond 'elke korte transmissietijd') - 0 of 1. Het signaaloogdiagram (dat je kunt zien als een 'helderheid'-diagram van het signaal) is een groot 'oog', wat erg intuïtief is.

PCIe 6.0 maakt echter voor het eerst gebruik van PAM4-codering (Four-Level Pulse Amplitude Modulation). Het voordeel is dat het 2 bits per intervaleenheid kan verzenden, wat overeenkomt met vier niveaus: 00, 01, 10 en 11. Als gevolg hiervan wordt het signaaloogdiagram drie op elkaar gestapelde kleine "ogen", wat overeenkomt met het passen van twee keer zoveel informatie in dezelfde hoeveelheid tijd.

Veel mensen vragen zich misschien af: hoe kan PAM4 de snelheid verdubbelen zonder de frequentie te verhogen?

Het is eigenlijk heel simpel: de Nyquist-frequentie van PCIe 5.0 is 16GHz (de helft van 32GT/s). Nadat PCIe 6.0 PAM4 heeft overgenomen, blijft de Nyquist-frequentie 16GHz, hoewel de snelheid verdubbelt tot 64GT/s, omdat deze 1 extra bit per intervaleenheid verzendt. Dit betekent dat de fundamentele frequentie van het signaal niet verandert, zodat de frequentievereisten voor de printplaat (PCB) en connectoren niet significant toenemen, en de transmissieafstand vergelijkbaar kan zijn met die van 5.0, zonder dat het hardwaretransmissieontwerp hoeft te worden gewijzigd.

Maar er is geen gratis lunch – PAM4 heeft ook zijn tekortkomingen, die we duidelijk moeten maken:

1. Verminderde signaalhelderheid: de algehele spanningsamplitude staat vast en elk van de drie 'kleine ogen' van de PAM4 is slechts een derde van de hoogte van het 'grote oog' van NRZ. Theoretisch is de signaalhelderheid (signaal-ruisverhouding) van PAM4 ongeveer 9,5 dB slechter dan die van NRZ, wat simpelweg betekent dat het gevoeliger is voor interferentie.

2. Zwakker anti-interferentievermogen: Of het nu gaat om interferentie van de voeding, overspraak tussen signalen of signaalreflectie, het is allemaal waarschijnlijker dat ze bitfouten (datatransmissiefouten) veroorzaken in een PAM4-systeem.

3. Moeilijker testen: In het verleden vereisten testsignalen slechts het meten van één 'groot oog', maar nu moeten we drie 'kleine ogen' meten en aandacht besteden aan nieuwe indicatoren zoals lineariteit (RLM), waardoor de moeilijkheidsgraad en de kosten van het testen aanzienlijk toenemen.

2. Datastroomstructuur: Flit-modus is verplicht

PCIe 5.0 gebruikt nog steeds de oude methode: 128b/130b-codering, die een "overhead" heeft van ongeveer 1,5% (wat betekent dat je bij het verzenden van gegevens een beetje extra irrelevante hulpinhoud moet verzenden). Het ondersteunt ook TLP-pakketten (data-"pakketten" voor verzending) van verschillende groottes, een modus die "Non-Flit" wordt genoemd. Elk "pakket" heeft zijn eigen controle (CRC), wat overeenkomt met een exclusief "anti-namaaklabel" voor elk pakket.

Om PAM4-codering te matchen met de FEC-foutcorrectietechnologie die we later zullen bespreken, moet PCIe 6.0 de Flit-modus inschakelen (eenvoudig gezegd: "datapakketten" met een vaste grootte). Een Flit is een datablok met een vaste lengte (256 bytes) en de interne structuur ervan is duidelijk en kan worden opgesplitst in:

- 235 bytes TLP: de kerngegevens die daadwerkelijk moeten worden verzonden

- 6 bytes DLP: komt overeen met een "middenlaaglabel" voor de gegevens, verantwoordelijk voor de transmissieverbinding op de linklaag

- 8 bytes CRC: een controlecode die wordt gebruikt om te verifiëren of de gegevens correct zijn verzonden

- 6 bytes FEC: "Back-upgegevens" voor foutcorrectie, die we later in detail zullen uitleggen

Veel mensen vragen zich misschien af: waarom moeten we "pakketten" met een vaste grootte gebruiken? De redenen zijn simpel, slechts drie punten:

1. Handig voor FEC-foutcorrectie: FEC-foutcorrectie wordt berekend in blokken met een vaste lengte, en een Flit is precies een complete verwerkingseenheid. Je hoeft hem niet te splitsen, waardoor hij efficiënter wordt.

2. Minder overhead: de oude extra overheadkosten, zoals synchronisatieheaders en framingtokens, zijn geoptimaliseerd. Hoewel de pakketten een vaste grootte hebben, wordt het algehele bandbreedtegebruik feitelijk verbeterd.

3. Gemakkelijkere foutafhandeling: eerst repareert FEC ter plekke kleine corrigeerbare fouten, waarna CRC opnieuw controleert. Als het probleem niet kan worden opgelost, wordt er een hertransmissie gestart. Het proces is duidelijk en brengt geen heen en weer gedoe met zich mee.

3. Bitfoutpercentage en foutcorrectiemechanisme: nieuw toegevoegde FEC-foutcorrectiefunctie

PCIe 5.0 stelt zeer strenge eisen aan datatransmissiefouten: de end-to-end bit error rate (eenvoudigweg de kans op onjuiste datatransmissie) mag niet groter zijn dan 1E-12, wat betekent dat er maximaal 1 bitfout is voor elke 1 biljoen verzonden bits. Het is gebaseerd op fysieke laag-equalisatietechnologie plus hertransmissie van de linklaag, zonder speciale foutcorrectiefunctie.

Omdat PAM4-codering inherent gevoeliger is voor bitfouten, voegt PCIe 6.0 specifiek een lichtgewicht voorwaartse foutcorrectie toe (afgekort FEC; in de volksmond "error correction backup" gedragen tijdens de verzending). De specificatie definieert ook een nieuwe indicator genaamd FBER (First Bit Error Rate), waarvoor ≤ 1E-6 vereist is. Hoewel dit losser lijkt dan de eis van 5.0, is het algehele foutcorrectievermogen met FEC-ondersteuning feitelijk sterker.

Hoe werkt FEC? Het is eenvoudig: bij het verzenden van gegevens worden voor elke Flit 6 bytes FEC-redundante informatie (d.w.z. "back-upgegevens") berekend en meegestuurd. Na ontvangst gebruikt de ontvanger eerst FEC om kleine corrigeerbare fouten ter plekke te herstellen. Als de fout te groot is om door FEC te worden opgelost, detecteert CRC deze en start een hertransmissie.

De voordelen van dit tweestapsmechanisme van "Eerst FEC voor foutcorrectie, daarna CRC voor foutverificatie" zijn bijzonder duidelijk:

- De meeste kleine fouten van één bit kunnen rechtstreeks door FEC worden opgelost zonder opnieuw te verzenden, waardoor de latentie onder controle blijft en de algehele snelheid niet wordt vertraagd.

- De waarschijnlijkheid van hertransmissie is zeer laag, gecontroleerd binnen 5E-6, en het extra bandbreedteverbruik bedraagt slechts ongeveer 0,05%, wat nauwelijks invloed heeft op het normale gebruik.

- Vergeleken met de RS-FEC van Ethernet (latentie van ongeveer 100 nanoseconden) heeft de lichtgewicht FEC van PCIe 6.0 een veel lagere latentie en heeft deze geen invloed op de normale werking van apparaten.

4. Egalisatie van de ontvanger: aanzienlijke verbetering van de foutcorrectiemogelijkheden

Tijdens signaaloverdracht op hoge snelheid zullen de signalen zwakker worden, net zoals geluid stiller wordt naarmate het verder reist. Op dit moment is ter compensatie "equalisatie"-technologie nodig, waardoor de ontvanger het signaal duidelijk kan ontvangen. PCIe 5.0's referentie-DFE (Decision Feedback Equalization, een type foutcorrectietechnologie) heeft 3 tikken, wat overeenkomt met slechts 3 "foutcorrectie-assistenten".

Omdat PAM4-signalen gevoeliger zijn voor interferentie, stelt PCIe 6.0 hogere eisen aan de foutcorrectiemogelijkheden. De referentie-DFE springt naar 16 tikken, wat overeenkomt met meerdere malen meer 'foutcorrectie-assistenten'. De digitale signaalverwerkingscapaciteit van de ontvanger is ook aanzienlijk verbeterd, waardoor ‘staartinterferentie’ (de extra interferentie die overblijft na signaaloverdracht) beter kan worden geëlimineerd.

Bovendien is CTLE (Continuous Time Linear Equalization) ook geüpgraded, van 4 polen/2 nullen naar 6 polen/3 nullen, met een sterker vermogen om signaalverzwakking te compenseren.

Veel mensen vragen zich misschien af: waarom hebben we zoveel "foutcorrectie-assistenten" (tikken) nodig? Omdat de drie "kleine ogen" van PAM4 verschillende egalisatievereisten hebben, vooral de bovenste en onderste ogen, die gevoeliger zijn voor niet-lineaire interferentie. Alleen een sterkere DFE kan alle drie de "kleine ogen" zo afstellen dat ze helder zijn, zodat het signaal normaal kan worden ontvangen.

5. Signaalintegriteit: strengere eisen, geen ruimte voor compromissen

Uit de parametertabel hierboven blijkt duidelijk dat de testvereisten van PCIe 6.0 veel strenger zijn dan die van 5.0. Laten we eens kijken hoe streng ze precies zijn, één voor één:

- Rx-test ooghoogte: verlaagd van 15 mV in 5,0 naar 6 mV in 6,0 (alleen voor het bovenste oog), wat overeenkomt met meer dan een verdubbeling van de "helderheidsnorm" voor signalen.

- Rx-test oogbreedte: verlaagd van 9,375 ps in 5,0 naar 3,125 ps in 6,0 (nog steeds voor het bovenste oog), wat ook de vereiste voor tijdnauwkeurigheid aanzienlijk vergroot.

- Vereiste referentieklokjitter: aangescherpt van ≤0,25ps RMS naar ≤0,15ps RMS. Simpel gezegd is de vereiste klokstabiliteit hoger, zonder ruimte voor afwijkingen.

- Kanaalverliesbudget: verlaagd van 36 dB bij 16 GHz naar 32 dB bij 16 GHz, wat betekent dat de signaalverzwakking tijdens verzending niet te groot kan zijn en dat de hardwarevereisten strenger zijn.

Dit betekent dat ontwerpen die "goed genoeg" waren in het PCIe 5.0-tijdperk volledig nutteloos zullen zijn in het 6.0-tijdperk. Elk gat in de printplaat, elke millimeter bedrading en elke connector moet nauwkeurig worden gecontroleerd – er is geen ruimte voor onzorgvuldigheid.

Er zijn hier verschillende belangrijke uitdagingen, die ik voor iedereen zal benadrukken:

1. PCB-materiaal: Er moeten materialen met ultralaag verlies worden gebruikt, zoals MEGTRON 7 en RO4835. Gewone FR-4-materialen die we gewoonlijk gebruiken, zijn niet bestand tegen signaalverzwakking op 32GHz en zullen bij gebruik gemakkelijk fouten bij de gegevensoverdracht veroorzaken.

2. Connectoren: Opbouwconnectoren zijn standaard geworden en het perspassingproces moet uiterst nauwkeurig zijn. Een kleine afwijking zal het signaal beïnvloeden en een onstabiele transmissie veroorzaken.

3. Stabiliteit van de voeding: PAM4 is erg gevoelig voor interferentie van de voeding. Het vorige ontwerp van de stroomvoorziening kon helemaal niet aan de eisen voldoen, dus moet het stroomdistributienetwerk (PDN) opnieuw worden ontworpen om een stabiele stroomvoorziening te garanderen.

4. Overspraakcontrole: de afstand tussen differentiële paren, de via's van afgeschermde aarde: elk detail kan niet worden weggelaten. Een kleine onoplettendheid zal overspraak tussen signalen veroorzaken en de transmissiekwaliteit beïnvloeden.

6. Commerciële vooruitzichten: eerst op ondernemingsniveau, daarna op consumentenniveau

Vanuit praktisch toepassingsperspectief is de positionering van deze twee generaties producten heel verschillend. Laten we het in twee categorieën opsplitsen, zodat iedereen het in één oogopslag kan begrijpen.

PCIe 5.0 is nu volledig populair in AI-servers en datacenters. Of het nu gaat om de grafische kaarten uit de RTX 50-serie van NVIDIA, de grafische kaarten uit de RX 9000-serie van AMD of solid-state drives (SSD's) van ondernemingskwaliteit, ze ondersteunen allemaal PCIe 5.0 en worden veel gebruikt.

Daarentegen verloopt de commercialisering van PCIe 6.0 relatief traag. Hoewel de specificatie begin 2022 werd vrijgegeven, zullen de daadwerkelijk beschikbare apparaten pas in 2026 op de markt komen. Daar zijn drie belangrijke realistische redenen voor:

1. Hoge kosten: de tape-outkosten van een PCIe 6.0-controller bedragen ongeveer 20-35 miljoen dollar, twee keer zoveel als die van 5.0. Fabrikanten hebben hoge investeringskosten en zullen het niet gemakkelijk in massaproductie brengen.

2. Hoge technische drempel: PAM4-ontwerp, productverificatie en testen vereisen allemaal een geheel nieuwe toolchain. Veel fabrikanten hebben deze technologie nog niet onder de knie en kunnen in korte tijd geen gekwalificeerde producten produceren.

3. Uiteenlopende eisen: AI- en high-performance computing (HPC)-datacenters hebben echt de hoge bandbreedte van PCIe 6.0 nodig voor snellere gegevensoverdracht en hogere efficiëntie. Voor gewone consumentencomputers en gameconsoles is er echter vrijwel geen vraag naar 6.0; de huidige PCIe 5.0 SSD's zijn al zo snel dat gebruikers het verschil niet kunnen waarnemen; hogere snelheden zijn niet nodig.

Volgens prognoses van de sector zal PCIe 6.0 wellicht pas na 2030 populair zijn op de consumentenmarkt. Maar op het gebied van ondernemingen, met name AI-servers, zal de grootschalige implementatie in 2026-2027 beginnen, en voor het eerst op professionele terreinen terechtkomen.

Samenvatting: Het essentiële verschil tussen de twee generaties

Terug naar de oorspronkelijke vraag: wat is het echte verschil tussen PCIe 5.0 en 6.0?

Om het in gewone taal samen te vatten: 5.0 is het plafond van het NRZ-coderingstijdperk, dat oude technologie tot het uiterste drijft; terwijl 6.0 het startpunt is van het PAM4-coderingstijdperk, waardoor een geheel nieuwe technische route wordt geopend.

Dimensie | PCIe 5.0 | PCIe 6.0 |

Technische essentie | NRZ-codering tot het uiterste gedreven | Overschakelen naar de nieuwe PAM4-coderingstrack |

Signaalkarakteristieken | Eén "groot oog", duidelijk signaal | Drie "kleine ogen", gevoelig voor interferentie |

Foutcorrectiemechanisme | Vertrouwt op CRC-controle; wordt opnieuw verzonden als er een fout is opgetreden | FEC corrigeert eerst; wordt opnieuw verzonden als het niet kan worden opgelost |

Ontwerp moeilijkheidsgraad | Hoog, maar beheersbaar | Extreem hoog, met een hoge technische drempel |

Testvereisten | Streng; volg gewoon de normen | Extreem streng; geen ruimte voor detailfouten |

Toepassingsscenario's | Populair in AI-servers; ook bruikbaar voor consumentenkwaliteit | Net begonnen op ondernemingsniveau; consumentenkwaliteit om te wachten |

Voor ingenieurs test het werken aan PCIe 5.0 hun vermogen om oude technologieën te verfijnen en te perfectioneren; Het werken aan PCIe 6.0 test hun vermogen om nieuwe technologieën te leren en zich aan nieuwe routes aan te passen. Voor de hele sector is 5.0 een volwassen technologie die vandaag de dag bruikbaar en betrouwbaar is, terwijl 6.0 de toekomstige richting is. Deze toekomst zal echter eerst vanuit datacenters komen en dan langzaam zijn weg vinden naar de levens van gewone gebruikers.

|(Opmerking: delen van het document kunnenAIgenereren)