Produttore di cavo dati di alta qualità

Produttore di cavo dati di alta qualità

Epigrafe: Da 32GT/s a 64GT/s, può sembrare solo un raddoppio della velocità, ma dietro c'è una completa trasformazione del percorso tecnico.

Introduzione: molto più che raddoppiare la velocità

Dopo aver lavorato per così tanti anni nel settore dei server AI e dei data center, la domanda che mi viene posta più spesso è: qual è la vera differenza tra PCIe 5.0 e 6.0? Non sta semplicemente raddoppiando la velocità?

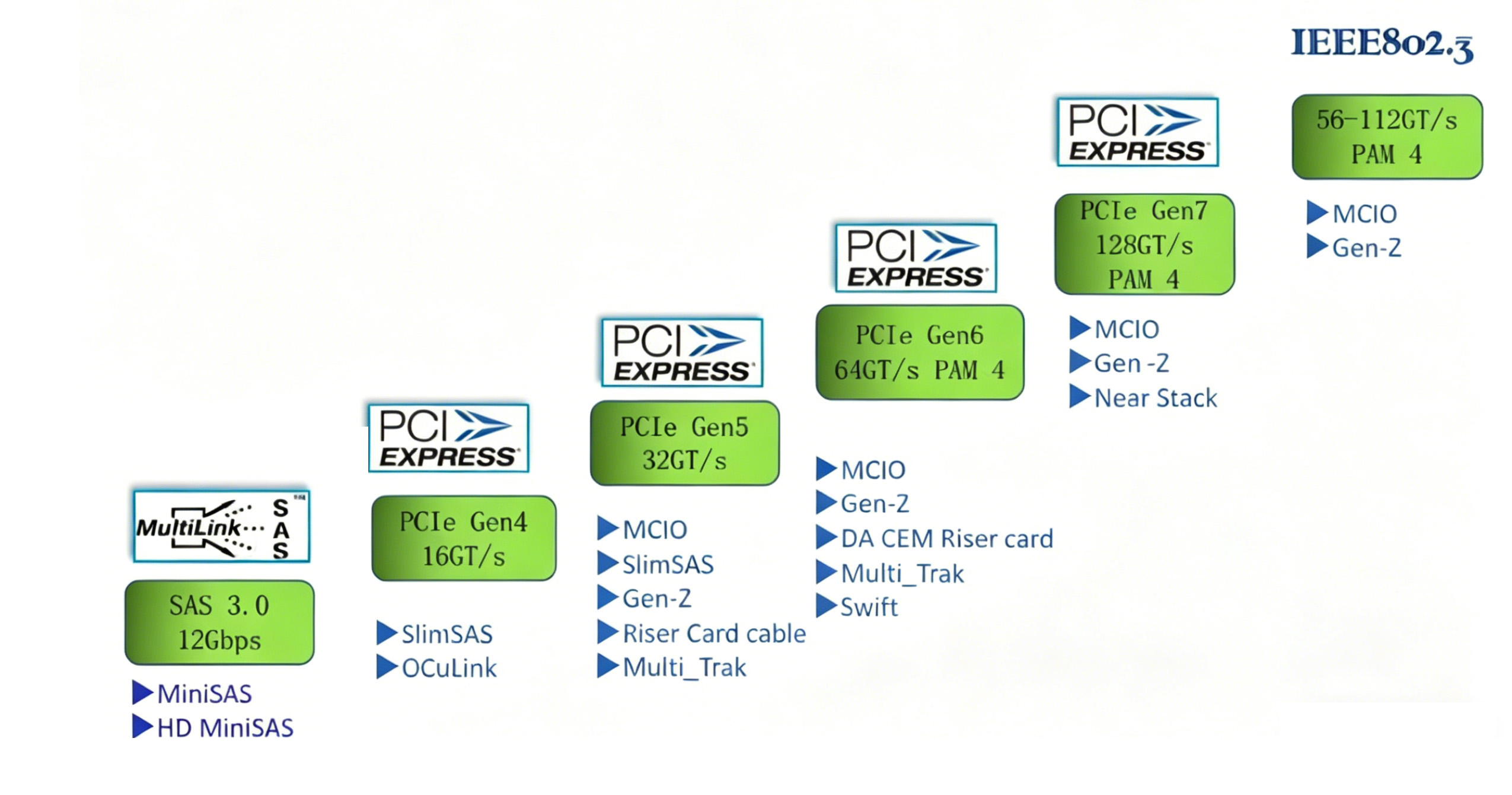

Ogni volta che sento questa domanda, devo spiegarla a tutti: l'aggiornamento da PCIe 5.0 a 6.0 è molto più drammatico rispetto alle generazioni precedenti. Da 3.0 a 4.0 e da 4.0 a 5.0, sebbene anche la velocità sia raddoppiata, il percorso tecnico è rimasto sostanzialmente lo stesso: entrambi utilizzavano la codifica NRZ e architetture di equalizzazione simili. Ma dalla versione 5.0 alla 6.0 l'intera base tecnica dello strato fisico è stata completamente sostituita.

Per aiutare tutti a capire quanto sia completo questo aggiornamento, ho messo insieme un confronto dettagliato facile da capire, senza bisogno di pensarci troppo.

Innanzitutto, ecco una tabella di confronto dei parametri principali, così puoi vedere le differenze a colpo d'occhio:

Dimensione di confronto | PCIe 5.0 | PCIe 6.0 | Modifica intervallo |

Velocità dati | 32 GT/s | 64 GT/s | Raddoppiato |

x16 Larghezza di banda bidirezionale | 128 GB/s | 256GB/s | Raddoppiato |

Metodo di codifica | NRZ (PAM2) | PAM4 | Nuovo formato di modulazione |

Frequenza di Nyquist | 16GHz | 16GHz | Rimane invariato |

Bit per interfaccia utente | 1 po' | 2 bit | Raddoppiato |

Schema di codifica | 128b/130b | 1b/1b (modalità veloce) | Completamente Ristrutturato |

Correzione degli errori in avanti (FEC) | Nessuno | FEC leggero | Meccanismo appena aggiunto |

Unità di controllo del flusso | Non-Flit (pacchetto variabile) | Svolazza (256 byte fissi) | Modalità appena aggiunta |

Requisito del tasso di errore in bit | BER ≤ 1E-12 | FBER ≤ 1E-6 | Nuovo indicatore metrico |

Bilancio delle perdite di canale | 36 dB a 16 GHz | 32 dB a 16 GHz | Leggermente stretto |

Test Rx Altezza degli occhi | 15 mV | 6 mV (occhio superiore) | Significativamente ridotto |

Test Rx Larghezza occhi | 9.375 PS | 3.125 ps (occhio superiore) | Significativamente ridotto |

Riferimento CTLE | 4 poli/2 zeri | 6 poli/3 zeri | Capacità di equalizzazione migliorata |

DFE di riferimento | 3 rubinetti | 16 rubinetti | Notevolmente migliorato |

Successivamente, analizzerò cosa c'è dietro ciascuna di queste differenze una per una, utilizzando sempre un linguaggio semplice, senza gerghi oscuri, quindi garantisco che tutti possano capirlo.

1. Metodo di codifica: un passaggio fondamentale da NRZ a PAM4

Questa è la differenza fondamentale tra le due generazioni e, una volta compresa questa, tutte le altre differenze saranno facili da comprendere.

PCIe 5.0 e tutte le versioni precedenti utilizzano la codifica NRZ, nota anche come codifica Non-Return-to-Zero o PAM2 in breve. In poche parole, invia 1 bit per intervallo unitario (colloquialmente, "ogni breve tempo di trasmissione"): 0 o 1. Il diagramma dell'occhio del segnale (che puoi considerare come un diagramma di "chiarezza" del segnale) è un grande "occhio", che è molto intuitivo.

PCIe 6.0, tuttavia, utilizza per la prima volta la codifica PAM4 (Four-Level Pulse Amplitude Modulation). Il suo vantaggio è che può inviare 2 bit per intervallo unitario, corrispondenti a quattro livelli: 00, 01, 10 e 11. Di conseguenza, il diagramma dell'occhio del segnale diventa tre piccoli "occhi" impilati insieme, il che equivale a inserire il doppio delle informazioni nello stesso periodo di tempo.

Molte persone potrebbero chiedersi: come può PAM4 raddoppiare la velocità senza aumentare la frequenza?

In realtà è abbastanza semplice: la frequenza Nyquist di PCIe 5.0 è 16GHz (metà di 32GT/s). Dopo che PCIe 6.0 ha adottato PAM4, anche se la velocità raddoppia a 64GT/s, la frequenza Nyquist rimane a 16GHz, perché trasmette 1 bit in più per intervallo unitario. Ciò significa che la frequenza fondamentale del segnale non cambia, quindi i requisiti di frequenza per il circuito stampato (PCB) e i connettori non aumentano in modo significativo e la distanza di trasmissione può essere simile a quella di 5.0, senza la necessità di modificare la progettazione della trasmissione hardware.

Ma non c’è niente da fare: anche PAM4 ha i suoi difetti, che dobbiamo chiarire:

1. Chiarezza del segnale ridotta: l'ampiezza complessiva della tensione è fissa e ciascuno dei tre "occhi piccoli" di PAM4 è solo un terzo dell'altezza dell'"occhio grande" di NRZ. Teoricamente, la chiarezza del segnale (rapporto segnale-rumore) di PAM4 è circa 9,5 dB peggiore di quella di NRZ, il che significa semplicemente che è più suscettibile alle interferenze.

2. Abilità anti-interferenza più debole: che si tratti di interferenze nell'alimentazione, diafonia tra segnali o riflessione del segnale, tutti hanno maggiori probabilità di causare errori di bit (errori di trasmissione dati) in un sistema PAM4.

3. Test più problematici: in passato, testare i segnali richiedeva solo la misurazione di un "occhio grande", ma ora dobbiamo misurare tre "occhi piccoli" e prestare attenzione a nuovi indicatori come la linearità (RLM), che aumenta significativamente la difficoltà e il costo dei test.

2. Struttura del flusso di dati: la modalità Flit è obbligatoria

PCIe 5.0 utilizza ancora il vecchio metodo: codifica 128b/130b, che ha un "overhead" di circa l'1,5% (il che significa che quando si trasmettono dati, è necessario inviare un po' di contenuto ausiliario extra irrilevante). Supporta anche pacchetti TLP ("pacchetti" di dati per la trasmissione) di diverse dimensioni, una modalità chiamata "Non-Flit". Ogni "pacchetto" è dotato di un proprio controllo (CRC), che equivale ad un'esclusiva "etichetta anticontraffazione" per ogni pacchetto.

Per abbinare la codifica PAM4 e la tecnologia di correzione degli errori FEC di cui parleremo più avanti, PCIe 6.0 deve abilitare la modalità Flit (in poche parole, "pacchetti di dati" di dimensione fissa). Un Flit è un blocco dati di lunghezza fissa, 256 byte, e la sua struttura interna è chiara e si suddivide in:

- 235 byte di TLP: i dati fondamentali che effettivamente devono essere trasmessi

- 6 byte di DLP: equivalente a una "etichetta di livello intermedio" per i dati, responsabile della connessione di trasmissione del livello di collegamento

- 8 byte di CRC: Un codice di controllo utilizzato per verificare se i dati sono stati trasmessi correttamente

- 6 byte di FEC: "Dati di backup" per la correzione degli errori, che spiegheremo in dettaglio più avanti

Molte persone potrebbero chiedersi: perché dobbiamo usare "pacchetti" di dimensioni fisse? Le ragioni sono semplici, bastano tre punti:

1. Comodo per la correzione degli errori FEC: la correzione degli errori FEC viene calcolata in blocchi di lunghezza fissa e un Flit è esattamente un'unità di elaborazione completa, senza bisogno di dividerla, rendendola più efficiente.

2. Riduzione dei costi generali: i vecchi costi aggiuntivi come le intestazioni di sincronizzazione e i token di framing sono stati ottimizzati. Sebbene i pacchetti abbiano dimensioni fisse, l'utilizzo complessivo della larghezza di banda è effettivamente migliorato.

3. Gestione degli errori più semplice: in primo luogo, FEC corregge piccoli errori correggibili sul posto, quindi CRC controlla nuovamente. Se non è possibile risolverlo, viene avviata una ritrasmissione. Il processo è chiaro e non comporta problemi avanti e indietro.

3. Tasso di errore bit e meccanismo di correzione degli errori: nuova funzione di correzione degli errori FEC

PCIe 5.0 ha requisiti molto severi per gli errori di trasmissione dei dati: il tasso di errore di bit end-to-end (semplicemente la probabilità di una trasmissione di dati errata) non deve superare 1E-12, ovvero al massimo 1 errore di bit per ogni trilione di bit trasmessi. Si basa sulla tecnologia di equalizzazione del livello fisico più ritrasmissione del livello di collegamento, senza una funzione di correzione degli errori dedicata.

Poiché la codifica PAM4 è intrinsecamente più soggetta a errori di bit, PCIe 6.0 aggiunge specificamente una leggera correzione degli errori in avanti (FEC in breve; colloquialmente, "backup di correzione degli errori" effettuato durante la trasmissione). La specifica definisce anche un nuovo indicatore chiamato FBER (First Bit Error Rate), che richiede ≤ 1E-6. Anche se questo sembra meno rigido rispetto ai requisiti della versione 5.0, con l’assistenza FEC la capacità complessiva di correzione degli errori è in realtà più forte.

Come funziona la FEC? È semplice: quando si inviano i dati, per ogni Flit vengono calcolati 6 byte di informazioni ridondanti FEC (ovvero "dati di backup") e inviati insieme ad esso. Dopo la ricezione, il ricevente utilizza innanzitutto la FEC per correggere piccoli errori correggibili sul posto. Se l'errore è troppo grande per essere corretto da FEC, CRC lo rileva e avvia una ritrasmissione.

I vantaggi di questo meccanismo in due fasi "prima FEC per la correzione degli errori, poi CRC per la verifica degli errori" sono particolarmente evidenti:

- La maggior parte dei piccoli errori a bit singolo possono essere corretti direttamente dal FEC senza ritrasmissione, mantenendo sotto controllo la latenza e senza rallentare la velocità complessiva.

- La probabilità di ritrasmissione è molto bassa, controllata entro 5E-6, e il consumo aggiuntivo di larghezza di banda è solo dello 0,05% circa, il che influisce a malapena sull'uso normale.

- Rispetto all'RS-FEC di Ethernet (latenza di circa 100 nanosecondi), il leggero FEC di PCIe 6.0 ha una latenza molto inferiore e non influisce sul normale funzionamento dei dispositivi.

4. Equalizzazione del ricevitore: miglioramento significativo nella capacità di correzione degli errori

Durante la trasmissione del segnale ad alta velocità, i segnali si attenuano, proprio come il suono diventa più debole man mano che viaggia. In questo momento, è necessaria la tecnologia di "equalizzazione" per compensare, consentendo al ricevitore di ricevere chiaramente il segnale. Il DFE di riferimento di PCIe 5.0 (Decision Feedback Equalization, un tipo di tecnologia di correzione degli errori) ha 3 tocchi, equivalenti a soli 3 "assistenti di correzione degli errori".

Poiché i segnali PAM4 sono più suscettibili alle interferenze, PCIe 6.0 ha requisiti più elevati per la capacità di correzione degli errori. Il DFE di riferimento passa a 16 tocchi, equivalenti a molti più "assistenti per la correzione degli errori". Anche la capacità di elaborazione del segnale digitale del ricevitore è notevolmente migliorata, essendo in grado di eliminare meglio le "interferenze di coda" (l'interferenza extra lasciata dopo la trasmissione del segnale).

Inoltre, è stato aggiornato anche il CTLE (Continuous Time Linear Equalization), da 4 poli/2 zeri a 6 poli/3 zeri, con una maggiore capacità di compensare l'attenuazione del segnale.

Molte persone potrebbero chiedersi: perché abbiamo bisogno di così tanti "assistenti per la correzione degli errori" (tap)? Perché i tre "occhi piccoli" di PAM4 hanno requisiti di equalizzazione diversi, in particolare gli occhi superiore e inferiore, che sono più suscettibili alle interferenze non lineari. Solo un DFE più potente può regolare tutti e tre gli "occhi piccoli" in modo che siano chiari, garantendo che il segnale possa essere ricevuto normalmente.

5. Integrità del segnale: requisiti più severi, nessuno spazio per compromessi

È chiaro dalla tabella dei parametri sopra che i requisiti di test di PCIe 6.0 sono molto più severi di quelli di 5.0. Analizziamo esattamente quanto sono severi, uno per uno:

- Altezza dell'occhio del test Rx: ridotta da 15 mV nella versione 5.0 a 6 mV nella versione 6.0 (solo per l'occhio superiore), che equivale a più che raddoppiare lo "standard di chiarezza" per i segnali.

- Larghezza occhi test Rx: ridotta da 9,375 ps nella versione 5.0 a 3,125 ps nella versione 6.0 (sempre per l'occhio superiore), il che aumenta notevolmente anche i requisiti di precisione temporale.

- Requisito di jitter dell'orologio di riferimento: ridotto da ≤0,25 ps RMS a ≤0,15 ps RMS. In poche parole, i requisiti di stabilità dell'orologio sono più elevati, senza spazio per deviazioni.

- Budget di perdita del canale: ridotto da 36 dB a 16 GHz a 32 dB a 16 GHz, il che significa che l'attenuazione del segnale durante la trasmissione non può essere eccessiva e i requisiti hardware sono più rigorosi.

Ciò significa che i progetti che erano "abbastanza buoni" nell'era PCIe 5.0 saranno completamente inutili nell'era 6.0. Ogni foro sul PCB, ogni millimetro di cablaggio e ogni connettore deve essere controllato con precisione, senza spazio per la disattenzione.

Ci sono diverse sfide chiave qui, che evidenzierò per tutti:

1. Materiale PCB: è necessario utilizzare materiali a bassissime perdite, come MEGTRON 7 e RO4835. I normali materiali FR-4 che utilizziamo abitualmente non possono sopportare l'attenuazione del segnale a 32 GHz e, se utilizzati, causeranno facilmente errori di trasmissione dei dati.

2. Connettori: i connettori a montaggio superficiale sono diventati standard e il processo di inserimento a pressione deve essere estremamente preciso. Una leggera deviazione influenzerà il segnale e causerà una trasmissione instabile.

3. Stabilità dell'alimentatore: PAM4 è molto sensibile alle interferenze dell'alimentatore. Il precedente progetto di alimentazione non è affatto in grado di soddisfare i requisiti, quindi la rete di distribuzione dell’energia (PDN) deve essere riprogettata per garantire un’alimentazione stabile.

4. Controllo della diafonia: la spaziatura delle coppie differenziali, i collegamenti di terra schermati: ogni dettaglio non può essere omesso. Una leggera svista causerà diafonia tra i segnali e influenzerà la qualità della trasmissione.

6. Prospettive commerciali: prima il livello aziendale, poi il livello consumer attenderà

Dal punto di vista dell’applicazione pratica, il posizionamento di queste due generazioni di prodotti è molto diverso. Dividiamolo in due categorie, in modo che tutti possano capirlo a colpo d'occhio.

PCIe 5.0 è ora pienamente popolare nei server e nei data center AI. Che si tratti delle schede grafiche della serie RTX 50 di NVIDIA, delle schede grafiche della serie RX 9000 di AMD o delle unità a stato solido (SSD) di livello aziendale, tutte supportano PCIe 5.0 e sono ampiamente utilizzate.

Al contrario, la commercializzazione di PCIe 6.0 è relativamente lenta. Sebbene le specifiche siano state rilasciate all’inizio del 2022, i dispositivi effettivamente disponibili non arriveranno sul mercato fino al 2026. Ci sono tre principali ragioni realistiche per questo:

1. Costo elevato: il costo di installazione del nastro di un controller PCIe 6.0 è di circa 20-35 milioni di dollari USA, il doppio di quello di un controller 5.0. I produttori hanno costi di investimento elevati e non li inseriranno facilmente nella produzione di massa.

2. Soglia tecnica elevata: la progettazione, la verifica del prodotto e i test di PAM4 richiedono tutti una toolchain completamente nuova. Molti produttori non hanno ancora padroneggiato questa tecnologia e non riescono a produrre prodotti qualificati in breve tempo.

3. Richieste divergenti: i data center AI e HPC (High Performance Computing) hanno davvero bisogno dell'elevata larghezza di banda di PCIe 6.0 per una trasmissione dei dati più rapida e una maggiore efficienza. Tuttavia, per i normali computer consumer e le console di gioco, non c’è quasi nessuna richiesta per 6.0: gli attuali SSD PCIe 5.0 sono già così veloci che gli utenti non riescono a percepire la differenza; velocità più elevate non sono necessarie.

Secondo le previsioni del settore, PCIe 6.0 potrebbe non essere popolare nel mercato consumer fino a dopo il 2030. Ma nel campo di livello aziendale, in particolare nei server AI, l’implementazione su larga scala inizierà nel 2026-2027, approdando inizialmente ai campi professionali.

Riepilogo: La differenza essenziale tra le due generazioni

Torniamo alla domanda originale: qual è la vera differenza tra PCIe 5.0 e 6.0?

Per riassumere in parole povere: 5.0 è il limite dell’era della codifica NRZ, spingendo la vecchia tecnologia al limite; mentre 6.0 è il punto di partenza dell'era della codifica PAM4, aprendo un percorso tecnico completamente nuovo.

Dimensione | PCIe 5.0 | PCIe 6.0 |

Essenza tecnica | Spingendo la codifica NRZ al limite | Passaggio alla nuova traccia di codifica PAM4 |

Caratteristiche del segnale | Un "grande occhio", segnale chiaro | Tre "occhi piccoli", suscettibili alle interferenze |

Meccanismo di correzione degli errori | Si basa sul controllo CRC; ritrasmette se c'è un errore | La FEC corregge prima; ritrasmette se non è possibile ripararlo |

Difficoltà di progettazione | Alto, ma gestibile | Estremamente elevato, con una soglia tecnica elevata |

Requisiti di prova | Rigoroso; basta seguire gli standard | Estremamente severo; non c'è spazio per errori di dettaglio |

Scenari applicativi | Popolare nei server AI; utilizzabile anche per il settore consumer | Livello aziendale appena iniziato; di tipo consumer, aspettare |

Per gli ingegneri, lavorare su PCIe 5.0 mette alla prova la loro capacità di affinare e perfezionare le vecchie tecnologie; lavorare su PCIe 6.0 mette alla prova la loro capacità di apprendere nuove tecnologie e di adattarsi a nuovi percorsi. Per l’intero settore, la 5.0 è una tecnologia matura, utilizzabile e affidabile oggi, mentre la 6.0 è la direzione futura, ma questo futuro arriverà prima dai data center, per poi farsi strada lentamente nella vita degli utenti comuni.

|(Nota: parti del documento potrebbero essereAIgenerare)